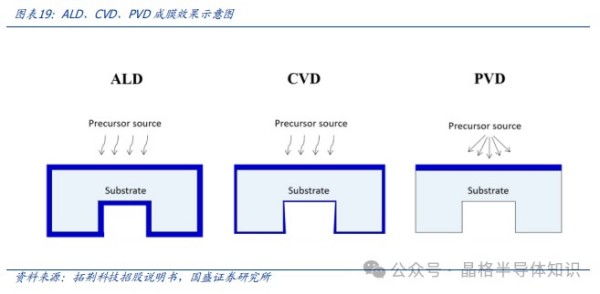

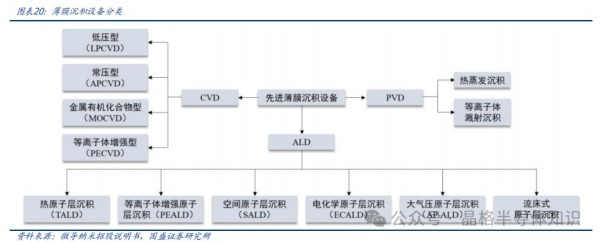

����ˇԭ����ͬ����Ĥ���e�O(sh��)��ɷ֞� PVD��CVD �� ALD����Ĥ���e���ڻ����ϳ��eһ�Ӽ{��(j��)�ı�Ĥ��������g�̺͒���ȹ�ˇ�ķ���(f��)�M(j��n)�У��������˺ܶ�ѯB����(l��i)�Č�(d��o)늻�^���ӣ�����ÿһ�Ӷ������O(sh��)Ӌ(j��)�õľ�(xi��n)·�D�������e��Ĥ���ϰ����������衢�����衢�ྦྷ��ȷǽ����Լ��~�Ƚ��١���Ĥ���e�O(sh��)����Ҫؓ(f��)؟(z��)����(g��)���E��(d��ng)�еĽ��|(zh��)���c���ٌӵij��e������ˇԭ����ͬ���ɷ֞� CVD�������W(xu��)������e���O(sh��)�䡢PVD�������������e���O(sh��)��/��?c��)O(sh��)��� ALD��ԭ�ӌӳ��e���O(sh��)�䡣

1��PVD������l���²�����������������Դ�����w��Һ�w������⻯�ɚ�B(t��i)ԭ�ӻ���ӣ�����x���x�ӣ���ͨ�^(gu��)�͉����w������x���w�����ڻ��w������e����ij�N����ܵı�Ĥ�ļ��g(sh��)��PVD �Ĥ���g(sh��)��Ҫ�֞����(l��i)��������l(f��)�Ĥ����՞R���Ĥ������x���Ĥ��PVD ���g(sh��)���L(zh��ng)�C(j��)����(ji��n)�Σ����e���ʸߣ���һ��ֻ�m����ƽ���Ĥ���Ƃ䡣

2��CVD��ͨ�^(gu��)���W(xu��)����(y��ng)�ķ�ʽ�����üӟᡢ���x�ӻ��ݗ��ȸ��N��Դ���ڷ���(y��ng)����(n��i)ʹ��B(t��i)��������B(t��i)�Ļ��W(xu��)���|(zh��)�ښ�����̽����Ͻ�(j��ng)���W(xu��)����(y��ng)�γɹ̑B(t��i)���e��ļ��g(sh��)����һ�Nͨ�^(gu��)���w��ϵĻ��W(xu��)����(y��ng)�ڻ��w������e��Ĥ�Ĺ�ˇ���ɑ�(y��ng)���ڽ^����Ĥ��Ӳ��ģ���Լ�����Ĥ�ӵij��e�����ձ�Ĥ���ϣ�CVD �֞���|(zh��)���W(xu��)������e��DCVD���ͽ��ٻ��W(xu��)������e��MCVD���ɴ��(l��i)��DCVD ��Ҫ�������x������(qi��ng)�ͻ��W(xu��)������e��PECVD�����γ������W(xu��)������e��SACVD�������|(zh��)ԭ�ӌӳ��e��DALD���ȡ�MCVD ��Ҫ�����͉����W(xu��)������e��LPCVD�����ЙC(j��)���ٻ��W(xu��)������e��MOCVD���ͽ���ԭ�ӌӳ��e��MALD���ȡ�

3)ALD��ԭ�ӌӳ��e���Ԍ����|(zh��)�Ԇ�ԭ��Ĥ��ʽһ��һ�ӵ��?c��)ڻ��ױ��档��ԭ�����f(shu��)��ALD ��ͨ�^(gu��)���W(xu��)����(y��ng)�õ���������ڳ��e����(y��ng)ԭ�������e����(y��ng)�l����Ҫ��ͳ��e�ӵ��|(zh��)���϶��c���y(t��ng)�� CVD ��ͬ������(du��)�ڂ��y(t��ng)�ij��e��ˇ���ԣ�ALD ��ˇ�������������L(zh��ng)�����c(di��n)���ɾ��_���Ʊ�Ĥ�ĺ�ȣ��Ƃ�ı�Ĥ���о���ĺ�Ⱥ̓�(y��u)����һ���ԣ��_(t��i)�A���w�ʸߣ��e�m����۽Y(ji��)��(g��u)�еı�Ĥ���L(zh��ng)��ALD �O(sh��)����e�ı�Ĥ���зdz����_��Ĥ����ƺͷdz���(y��u)Խ���_(t��i)�A���w�ʣ��� 28nm �����P(gu��n)�I�ߴ�sС���p�عˇ����ȡ����Խ��(l��i)Խ�V���đ�(y��ng)�ã�����e�� Spacer ���ϵČ��țQ���� Fin �Č��ȣ����Ƽs߉оƬ�Ƴ����M(j��n)�̶ȵĺ�������֮һ������֮�⣬ALD �O(sh��)���ڸ� k ���ϡ����ٖš�STI��BSI �ȹ�ˇ�о����ڴ�����(y��ng)�ã��V����(y��ng)���� CMOS �������惦(ch��)оƬ��TSV ���b�Ȱ댧(d��o)�w�����I(l��ng)��

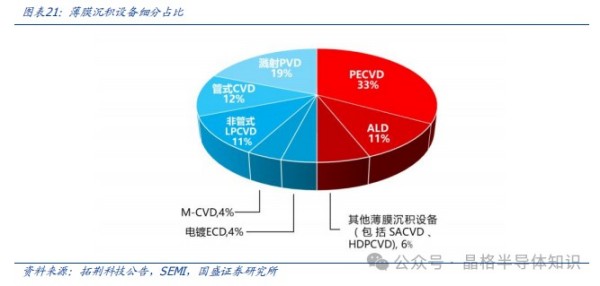

CVD �I(l��ng)�� PECVD �O(sh��)��ռ���^�ߣ�PVD �I(l��ng)����Ҫ��R�� PVD �O(sh��)�䡣�������W(xu��)������e��APCVD��������� CVD �O(sh��)�䣬�Y(ji��)��(g��u)��(ji��n)�Ρ����e���ʸߣ��V����(y��ng)���ڹ��I(y��)���a(ch��n)�С��͉����W(xu��)������e��LPCVD������ APCVD �Ļ��A(ch��)�ϰl(f��)չ����(l��i)�ġ����x���w����(qi��ng)���W(xu��)������e�O(sh��)�䣨PECVD���ڏā��װl(f��)չ�� 90nm �� IC ���켼�g(sh��)�^(gu��)���У���������Ҫ�Ľ�ɫ�����ڵ��x���w�����ã����W(xu��)����(y��ng)�ض����@���ͣ���Ĥ���ȵõ���ߣ����ܶȵ��Լӏ�(qi��ng)���Ǯ�(d��ng)ǰ��(y��ng)�����V���� CVD �O(sh��)�䣬�ڱ�Ĥ���e�O(sh��)����ռ���_(d��) 33%���γ������W(xu��)������e��SACVD����Ҫ��(y��ng)���ڜϲ���乤ˇ���� PVD �O(sh��)���У��R���O(sh��)��ռ��Ҫ���~��

�Y�ρ�(l��i)Դ��Դ����댧(d��o)�w֪�R(sh��)����̖(h��o)